3장. 순차 논리

1, 2장에서 만든 불 논리 침과 산술 칩들은 모두 조합 칩이라고 부른다.

이 조합 칩들은 중요한 기능을 하지만, 상태를 유지하지는 않는다.

컴퓨터는 값을 계산할 뿐 아니라 필요할 때마다 저장하고 다시 불러올 수 있어야 하므로, 시간이 지나도 데이터를 보존할 수 있는 메모리 소자가 필요하다. 이러한 메모리 소자는 순차 칩으로 만든다.

1. 배경

클록

대부분의 컴퓨터에서는 연속적으로 신호를 발생하는 마스터 클록으로 시간 진행을 표현한다.

보통 이 하드웨어는, 0-1 또는 고-저, 틱-톡 등으로 표시된 상태를 연속해서 오가는 발진기로 구현된다.

틱의 시작에서 톡까지 경과된 시간을 사이클이라 부르는데, 한 클록 사이클은 하나의 시간 단위 구분을 모델리한 것이다.

이 신호는 하드웨어의 회로망을 통해 컴퓨터에 있는 모든 순차 칩들에게 동시에 전달된다.

플립플롭

플립플롭은 1비트의 정보를 보관, 유지할 수 있는 회로이며 순차 회로의 기본요소이다.

정확히는 이전 상태를 계속 유지하며 저장한다.

이 기능은 2진 셀에서 레지스터, 임의 접근 기억장치(RAM)까지, 컴퓨터에서 상태를 유지하는 모든 하드웨어의 기초가 된다.

레지스터Register

레지스터는 시간이 지나도 값을 저장하고 로드할 수 있는 장치로, 기본적인 저장 기능인 out(t) = out(t-1)을 구현한 것이다.

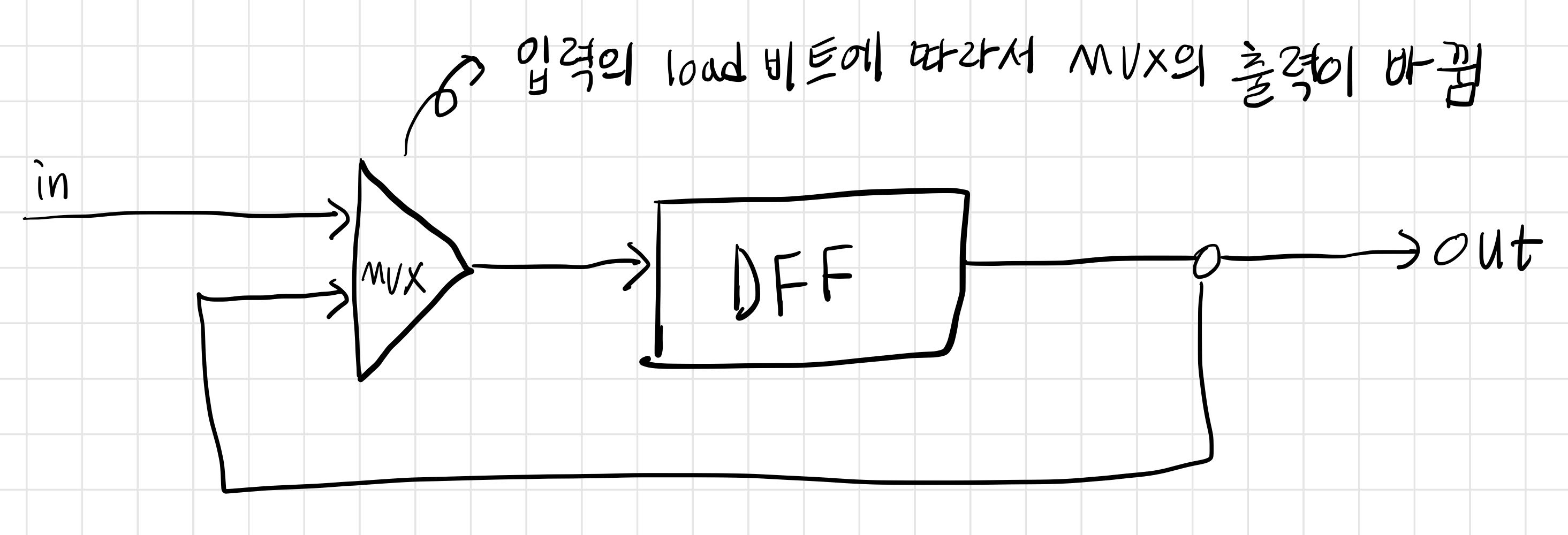

플립플롭과 비교하자면, 플립플롭은 바로 이전의 입력을 출력하기만 하는 장치지만 레지스터는 이전의 입력을 출력으로 보내주는 와중에 다시 한번 입력으로 보내주어 Mux(멀티플렉서)를 통해서 새로 들어온 입력의 load 비트를 감지하여 저장 유무를 정한다. 아래 사진은 1비트 레지스터를 그려본 것이다.

- 1-bit 레지스터

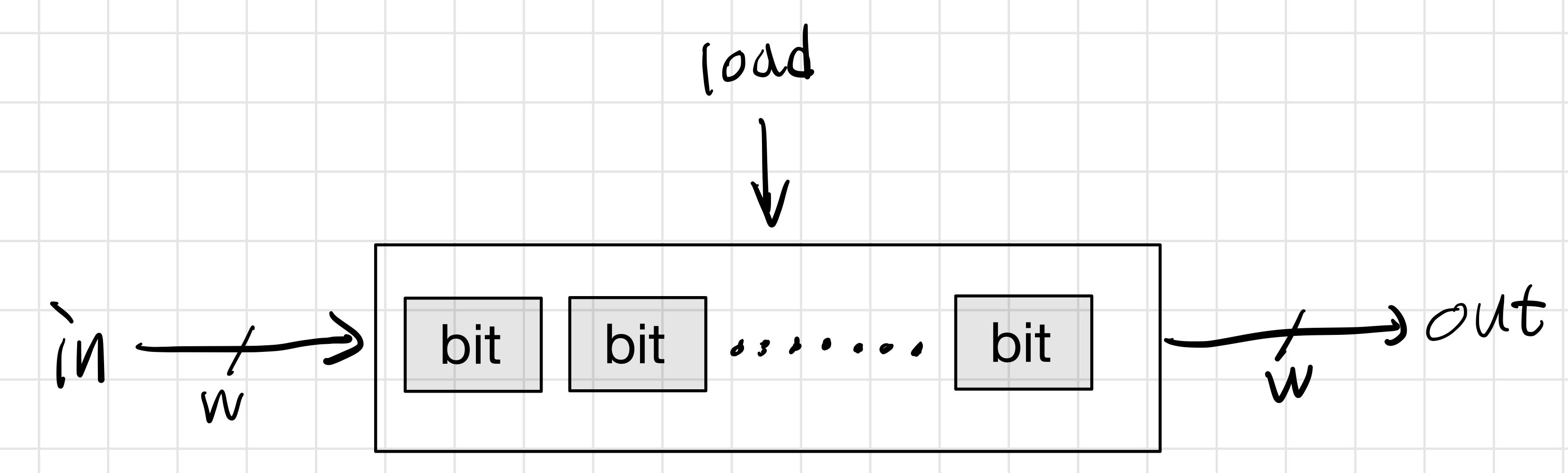

- multi-bit 레지스터

레지스터가 저장할 수 있는 비트의 개수는 폭(width)라고 부르며, 16, 32, 64비트가 그 폭을 뜻한다. 비트에 따라서 레지스터에 저장되는 멀티비트 값을 보통 단어(word)라고 부른다.

메모리Memory

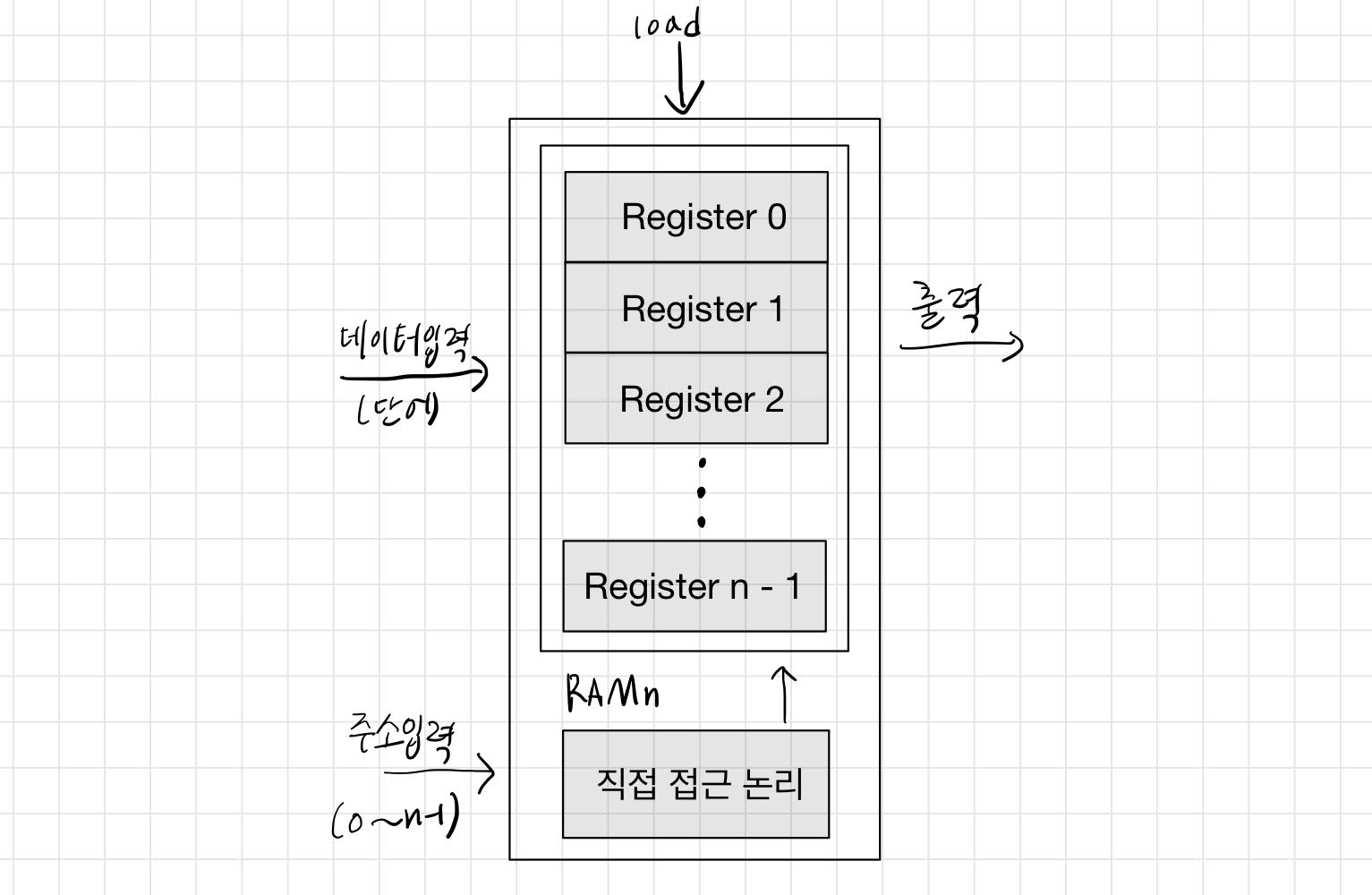

단어를 표현할 수 있게 되었으니 이제 임의의 길이의 메모리 뱅크(memory bank)를 구성할 수 있다.

아래의 그림은 임의 접근 메모리(Random Access Memory), 즉 램(RAM) 소자다. 임의 접근 메모리라는 용어는, 접근 순서와 관계없이 무작위로 선택된 단어를 읽고 쓸 수 있어서 붙은 말이다. 말하자면 물리적 저장 위치와 관계없이 어디든 똑같은 속도로 직접 접근이 가능하다는 뜻이다.

램은 멀티비트 레지스터를 나열해놓고 입력으로 데이터 입력, 주소 입력, 로드 비트라는 세 입력을 받는다.

주소 입력의 경우 읽기 연산(load=0)을 수행할 경우, 선택된 레지스터의 값을 바로 출력한다. 쓰기 연산(load=1) 때는 다음 사이클 때 선택된 메모리 레지스터에서 입력값을 받아, 해당 값을 출력하기 시작한다.

램의 기본 변수로는 각 단어의 비트 개수를 뜻하는 데이터 폭(width)과, RAM 내의 단어 수를 나타내는 크기(size)가 있다.

최신 컴퓨터는 32비트나 64비트면서 크기가 수억만개에 달하는 RAM들을 사용한다.

계수기counter

계수기는 매 시간 단위마다 내부 상태 값을 증가시키는 순차 칩으로 out(t)=out(t-1)+c라는 함수를 연산한다(c는 보통 1이다).

프로그램 계수기가 한가지 예로, 일반적으로 CPU에 탑재되어 다음에 실행해야 할 프로그램 명령의 주소를 출력하는 기능을 한다.

계수기 칩은 표준 레지스터의 입/출력 논리와, 상태 값에 상수를 더하는 논리가 조합된 것이다.

일반적으로 계수기에는 값을 0으로 다시 맞추거나, 새로운 계수 값을 불러오거나, 값을 증가시키는 대신 감소시키는 기능이 추가된다.

- 조합 논리와 순차 논리

시간 문제

지금까지 설명한 모든 칩들은 순차적이다.

간단히 말하자면, 순차 칩은 하나 이상의 DFF 게이트를 장착한 칩이다.

위에서 다시 순차 논리 이미지를 보면, 피드백 루프가 뒤의 조합논리에서 이전의 조합논리로 다시 되돌아간다.

조합 칩은 시간을 인지하지 못하기에 피드백 루프를 넣으면, 출력은 입력을... 입력을 출력을 따르므로 결국 자기 자신을 따라 결정된다는 문제가 생긴다.

반면에 순차 칩은 DFF로 인해서 시간 지연이 발생하기 때문에 출력을 문제없이 피드백할 수 있다.

이러한 순차 칩 출력의 시간지연으로 인해, 출력이 클록 사이클 단위로 변화하는 것을 이산화라고 한다.

이산화를 이용하여 전체 컴퓨터 아키텍처를 동기화 하는 데 활용할 수 있다.

x + y 연산을 하기위해, `ALU(산술 논리 연산 장치)`에 값을 전달해야 하는 상황이라면?

만약 x가 ALU와 물리적으로 가까워서 먼저 도착한다면,

조합 칩인 ALU는 시간 개념이 없으므로 다른 값이 들어오더라도 일단 더하고 볼 것이다.

그러나 순차 칩은 시간 지연이 가능하므로 이러한 문제에서 해방된다.